Makefile变量

在Makefile中使用变量有点类似于C语言中的宏定义,使用该变量相当于内容替换,使用变量可以使Makefile易于维护,修改起来变得简单。

Makefile有三种类型的变量:

- 普通变量

- 内置变量

- 自动变量

普通变量

- 变量定义直接用

= - 使用变量值用

$(变量名)

如:下面是变量的定义和使用

makefile

foo = abc #定义变量并赋值

bar = $(foo) #使用变量, $(变量名)定义了两个变量:foo、bar,其中bar的值是foo变量值的引用。

内置变量

除了使用用户自定义变量,Makefile中也提供了一些变量(变量名大写)供用户直接使用,内置变量就是内部定义好的变量,这些变量的含义是固定的

| 变量名 | 功能 | 默认含义 |

|---|---|---|

AR | 打包库文件 | ar |

AS | 汇编程序 | as |

CC | C编译器 | cc |

CPP | C预编译器 | $(CC) -E |

CXX | C++编译器 | g++ |

RM | 删除 | rm –f |

ARFLAGS | 库选项 | 无 |

ASFLAGS | 汇编选项 | 无 |

CFLAGS | C编译器选项 | 无 |

CPPFLAGS | C预编译器选项 | 无 |

CXXFLAGS | C++编译器选项 | 无 |

LDFLAGS | 链接器选项 | 无 |

自动变量

$@: 表示规则中的目标$<: 表示规则中的第一个条件$^: 表示规则中的所有条件,组成一个列表,以空格隔开,如果这个列表中有重复的项则消除重复项。

特别注意:。

模式规则

至少在规则的目标定义中要包含%,%表示一个或多个,在依赖条件中同样可以使用%,依赖条件中的%的取值取决于其目标:

比如: main.o:main.c add.o: add.c,说的简单点就是: xxx.o:xxx.c

实例

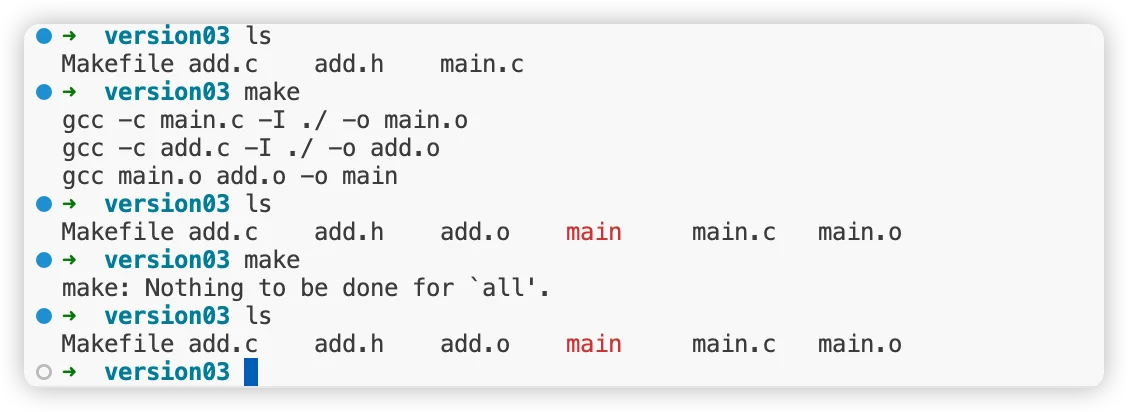

Makefile的第三个版本:

makefile

# 默认目标

all: main

target=main

obj=main.o add.o

CC=gcc

CFLAGS=-I ./

$(target):$(obj)

$(CC) $^ -o $@

%.o:%.c

$(CC) -c $< $(CFLAGS) -o $@c

#include "add.h"

#include <stdio.h>

int main(void) {

printf("%d\n", add(10, 20));

return 0;

}c

#ifndef __SYSS_ADD_H__

#define __SYSS_ADD_H__

int add(int a, int b);

#endif //__SYSS_ADD_H__c

#include "add.h"

int add(int a, int b) {

return a + b;

}执行make

缺点:冗余,若 .c 文件数量很多,编写起来比较麻烦,毕竟要写很多个 .o 文件名。